## ARCHITECTURAL SUPPORT FOR COPY AND TAMPER-RESISTANT SOFTWARE

A DISSERTATION SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING AND THE COMMITTEE ON GRADUATE STUDIES OF STANFORD UNIVERSITY IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

> David J. Lie December 2003

© Copyright by David J. Lie 2004 All Rights Reserved I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

> Dr. Mark Horowitz (Principal Adviser)

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

Dr. Dan Boneh

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

> Dr. Chandramohan A. Thekkath (Microsoft Research, Silicon Valley)

Approved for the University Committee on Graduate Studies.

### Abstract

Recently, there has been intense interest in the implementation of a trusted computing platform. Industry projects such as the Trusted Computing Platform Alliance, Microsoft's Palladium Project, and Intel's LaGrand Technologies all aim to embed hardware to support some amount of protection for applications so that they can be tamper-resistant.

In this work, we propose a new processor architecture called "XOM", which stands for eXecute Only Memory. XOM provides copy and tamper-resistance for software by supporting compartments, which protect both the code and data of programs. Compartments are implemented by a combination of architectural methods, in the form of on-chip access control tags, and cryptographic methods, in the form of ciphers and hashes that protect data off-chip. The trust model of the computing system is changed so that applications trust the hardware, instead of the operating system, to protect their code and data. A XOM processor was simulated by extending a MIPS-based processor model in the SimOS simulator.

An operating system, XOMOS, was constructed run on the XOM architecture. Because the applications do not trust the operating system with their data, this presents an interesting challenge for operating system design. This work shows that an untrusted operating system can be implemented on top of trusted hardware, such that the operating system has sufficient rights to manage resources, but does not have the rights to read or modify user application code or data. This is demonstrated by a port of the IRIX 6.5 operating system to the XOM processor, to create XOMOS. We were able to run some applications on XOMOS in our simulator and found overheads to be less than 5%.

We used a model checker to verify the security of the XOM processor architecture. A realistic "actual" processor was modeled along with an adversary, and compared against a "idealized" model that has no adversary. Inconsistencies between the two models are

flagged as failures in the protection guarantees that the processor aims to provide. We thus demonstrate that the processor is able to provide tamper-resistance, and that the most difficult attack to defend against is a memory replay attack.

## Acknowledgments

This work would not have been possible without the help and support of a large number of people.

First and foremost, I would like to thank my advisor, Prof. Mark Horowitz. There is little I can say to add to his already impeccable reputation as a researcher, scientist and teacher. As my supervisor, he has been patient and kind, and has always encouraged me to push myself further. It has truly been a privilege to work with him.

Dr. Chandramohan (Chandu) Thekkath has also been a great collaborator. He has generously donated his time and energy over the last four years. The numerous discussions we have had have been enjoyable, and I have benefited greatly from his knowledge of operating systems. I would also like to thank Prof. Dan Boneh, my associate advisor, who was responsible for sparking my interest in computer security and cryptography, as well as educating me in those fields. Thanks also go to Prof. John Mitchell, who always made himself available to proof read papers and help clarify my ideas. Prof. Dawson Engler and Prof. David Dill first introduced me to the concept of using formal techniques to check models for correctness, which subsequently proved very useful for my dissertation. Numerous thanks also go to Prof. Bill Dally, Prof. Mendel Rosenblum, Prof. Monica Lam, and President John Hennessey for allowing me to draw upon their experiences and technical knowledge.

This work would not have been possible without the support of Charles Orgish and Joe Little, who worked tirelessly to maintain a stable computing environment for research at the Computer Systems Laboratory at Stanford. Of no less importance has been the administrative support of Terry West, Deborah Harber, Taru Fisher, Penny Chumly, Teresa Lynn, Darlene Hadding, and Claire Ravi. I would also like to thank DARPA for their financial support, and Stanford University for providing fantastic facilities and a comfortable and relaxing environment, which allowed me to focus my attention on my research.

There are too many colleagues and friends to mention all who have made my time at Stanford memorable. Thus, in the limited space I will mention the graduate students whom I worked with in the Gates Building at Stanford. Robert Kunz and Jeff Gibson who worked next door helped show me my way around Stanford, helping me pass quals and giving me technical advice. They were good companions on the road as well, providing excellent company at conferences we attended. Andy Chou has also been a great friend and co-author, and I will always admire his patience and ability to write large amounts of code quickly, without sacrificing elegance and clarity. I would also like to thank Dean Liu, Francois Labonte, my office mates Alex Solomatnikov, and Amin Firoozshahian, as well as all the other members of the Horowitz group for their support and help.

I would like to thank the members of my family, who first encouraged me to apply and come to Stanford. And finally, words cannot express the gratitude I have for Xiaoli Liang, who has been my loving and caring companion for nearly all the time I have been at Stanford. It is impossible to imagine how this thesis would have been possible without her help and support.

# Contents

| A | bstrac | :t        |                                      | v   |

|---|--------|-----------|--------------------------------------|-----|

| A | cknov  | vledgmen  | ts                                   | vii |

| 1 | Intr   | oduction  |                                      | 1   |

|   | 1.1    | Overvie   | w of this Dissertation               | 4   |

| 2 | Cry    | ptograph  | ic Concepts                          | 6   |

|   | 2.1    | Compar    | tments                               | 6   |

|   | 2.2    | Symmet    | ric Ciphers                          | 7   |

|   | 2.3    | Asymme    | etric Ciphers                        | 8   |

|   | 2.4    | Message   | e Authentication Codes               | 9   |

| 3 | The    | XOM A     | rchitecture                          | 10  |

|   | 3.1    | The Abs   | stract XOM Machine                   | 12  |

|   |        | 3.1.1     | Supporting External Memory           | 14  |

|   |        | 3.1.2     | Supporting an Operating System       | 16  |

|   |        | 3.1.3     | Software Distribution Model          | 18  |

|   |        | 3.1.4     | Security                             | 20  |

|   | 3.2    | Virtual I | Machine Implementation               | 22  |

|   | 3.3    | A Hardy   | ware Implementation of a XOM Machine | 28  |

|   | 3.4    | The XO    | M Hardware Simulator                 | 37  |

|   | 3.5    | Mainten   | ance Issues                          | 39  |

|   |        | 3.5.1     | Processor Upgrade                    | 39  |

|   |      | 3.5.2     | Processor Key Recovery                                                                         | 40 |

|---|------|-----------|------------------------------------------------------------------------------------------------|----|

|   | 3.6  | Related   | d Work                                                                                         | 41 |

|   |      | 3.6.1     | Hardware Approaches                                                                            | 41 |

|   |      | 3.6.2     | Software Approaches                                                                            | 42 |

|   |      | 3.6.3     | Trusted Computing                                                                              | 42 |

|   | 3.7  | Summ      | ary                                                                                            | 44 |

| 4 | An ( | Operati   | ng System for the XOM Architecture                                                             | 46 |

|   | 4.1  | Operat    | ing System Design Issues                                                                       | 47 |

|   | 4.2  | XOM       | Key Table Support                                                                              | 48 |

|   |      | 4.2.1     | XOM Key Table System Calls                                                                     | 48 |

|   |      | 4.2.2     | Virtualizing the XOM Key Table                                                                 | 51 |

|   | 4.3  | Dealin    | g with Encrypted Data and MACs                                                                 | 52 |

|   |      | 4.3.1     | Saving and Restoring Context                                                                   | 52 |

|   |      | 4.3.2     | Paging Encrypted Memory                                                                        | 54 |

|   | 4.4  | Suppor    | rting Traditional Operating System Mechanisms                                                  | 56 |

|   |      | 4.4.1     | Shared Libraries                                                                               | 56 |

|   |      | 4.4.2     | Process Creation                                                                               | 57 |

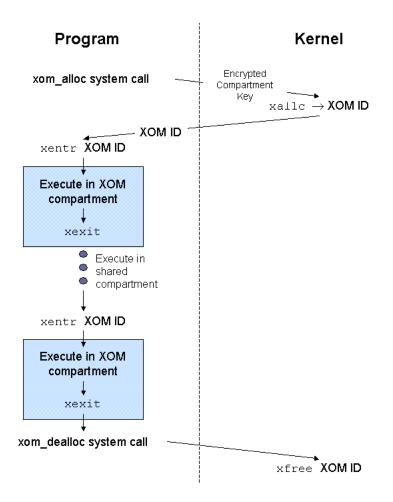

|   |      | 4.4.3     | User-defined Signal Handlers                                                                   | 59 |

|   | 4.5  | Costs of  | of Implementing XOMOS                                                                          | 61 |

|   |      | 4.5.1     | XOMOS Implementation Effort                                                                    | 63 |

|   |      | 4.5.2     | Operating System Performance Overhead                                                          | 64 |

|   |      | 4.5.3     | End-to-end Application Performance Overhead                                                    | 67 |

|   | 4.6  | Summ      | ary                                                                                            | 71 |

| 5 | Secu | irity Iss | ues                                                                                            | 73 |

|   | 5.1  | Attack    | Model                                                                                          | 73 |

|   | 5.2  | Hardw     | are Based Attacks                                                                              | 75 |

|   | 5.3  | Softwa    | re Based Attacks                                                                               | 76 |

|   | 5.4  | Forma     | Specification and Verification                                                                 | 79 |

|   |      | 5.4.1     | The Mur $\varphi$ Model Checker $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 80 |

|   |      | 5.4.2     | Abstracting the Instruction Set                                                                | 81 |

|    |                  | 5.4.3   | The Actual Model     | . 82  |

|----|------------------|---------|----------------------|-------|

|    |                  | 5.4.4   | The Idealized Model  | . 87  |

|    |                  | 5.4.5   | The Adversary        | . 89  |

|    |                  | 5.4.6   | Combining the Models | . 92  |

|    |                  | 5.4.7   | Verification Results | . 96  |

|    | 5.5              | Attack  | s not Covered by XOM | . 99  |

|    | 5.6              | Additi  | onal Security Issues | . 100 |

|    |                  | 5.6.1   | Key Revocation       | . 100 |

|    |                  | 5.6.2   | Privacy              | . 101 |

|    | 5.7              | Relate  | d work               | . 102 |

|    | 5.8              | Summ    | ary                  | . 102 |

| 6  | Con              | clusion | s and Future Work    | 103   |

|    | 6.1              | Future  | Work                 | . 105 |

| Bi | Bibliography 107 |         |                      | 107   |

# **List of Tables**

| 3.1 | Instructions in the Abstract XOM Machine               | 17 |

|-----|--------------------------------------------------------|----|

| 3.2 | XOM Simulator Parameters                               | 37 |

| 3.3 | Simulated XOM Instructions                             | 38 |

| 4.1 | Description of Simulated Instructions                  | 62 |

| 4.2 | XOMOS Kernel Implementation Effort                     | 63 |

| 4.3 | XOMOS User-code Implementation Effort                  | 63 |

| 4.4 | Overhead Due to New System Calls in XOMOS              | 65 |

| 4.5 | Micro-benchmark Instruction Overhead of XOMOS vs. IRIX | 66 |

| 4.6 | Micro-benchmark Cycle Overhead of XOMOS vs. IRIX       | 66 |

| 5.1 | User Instructions                                      | 82 |

| 5.2 | Privileged Instructions                                | 83 |

| 5.3 | Vulnerability from Caching MACs                        | 97 |

| 5.4 | Vulnerability from Incremental Hashes                  | 98 |

# **List of Figures**

| 3.1 | Compartments                                          | 11 |

|-----|-------------------------------------------------------|----|

| 3.2 | The Shared Compartment                                | 14 |

| 3.3 | Software Distribution in XOM                          | 19 |

| 3.4 | The XOM Virtual Machine Monitor (XVMM)]               | 25 |

| 3.5 | Memory Support for Secure Store                       | 28 |

| 3.6 | Memory Support for Secure Load                        | 29 |

| 3.7 | Valid Bits in the Caches                              | 30 |

| 3.8 | XOM Key Table Design                                  | 32 |

| 3.9 | A XOM Machine Implemented in Hardware                 | 35 |

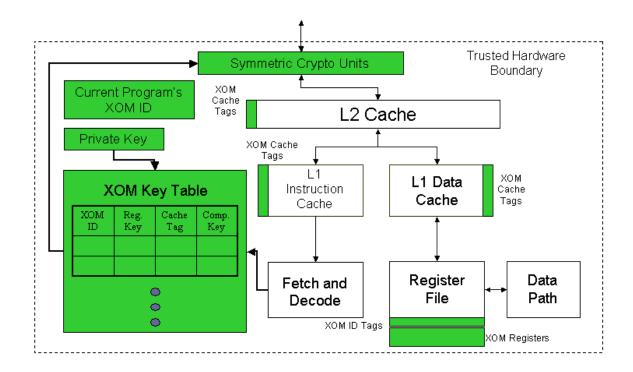

| 4.1 | Allocating and Using XOM Key Table entries            | 50 |

| 4.2 | XOMOS Context Switch Code                             | 54 |

| 4.3 | Exiting and Entering a Compartment for a Library Call | 58 |

| 4.4 | User-defined Signal Handler Support                   | 60 |

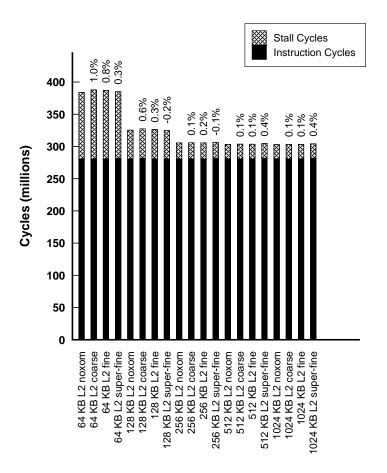

| 4.5 | Performance of XOM-mpeg                               | 68 |

| 4.6 | Performance of XOM-RSA                                | 69 |

| 5.1 | A Register Spoofing Attack                            | 77 |

| 5.2 | A Merkle Tree                                         | 79 |

## **Chapter 1**

## Introduction

There are many good reasons for creating tamper-resistant software including combating software piracy, enabling mobile code to run on untrusted platforms without the risk of tampering or intellectual property theft, and enabling the deployment of trusted clients in distributed services such as banking transactions, on-line gaming, electronic voting, and digital content distribution. Tamper-resistant software is also useful in situations where a portable device containing sensitive software and data may fall into the hands of adversaries, as well as for preventing viruses from modifying legitimate programs. This dissertation looks at one approach of providing this capability by modifying the base processor hardware to support programs that can only be executed, but cannot be read or modified. However, even without such a high level of tamper-resistance some applications assume it exists. For example, banking transactions still assume the tamper-resistance of software on the clients, even though there is no such assurance. While protocols such as Secure Sockets Layer (SSL), can reliably secure communications across the Internet, the user has no assurance that their web browser or underlying operating system is not maliciously monitoring or tampering with their transactions. If for example, a banking customer is unknowingly using a malicious web browser<sup>1</sup>, the web browser may record all of the customer's personal information and use that to impersonate the customer.

In another case, imagine the web browser is legitimate, but the underlying operating system has been compromised. The operating system may allow the banking customer

<sup>&</sup>lt;sup>1</sup>A customer may unknowingly download a modified client — in other words a Trojan Horse.

to initiate a transaction, but at an opportune time, simply hijack the network session by extracting the appropriate information from the address space of the web browser. This example shows that protecting the web browser from tampering is necessary, but not sufficient — it is also necessary to protect the web browser's execution from observation, otherwise the identity of the browser can be forged.

Systems can require various levels of tamper-resistance, which range from simply preventing an adversary from reading the instructions of a program, to protecting the instructions, data and execution of the program entirely. The level of security that an application requires depends on the sophistication of the adversary the system is intended to withstand. On the other hand, increased security may also require increased costs in performance overhead and hardware.

A very simple and cheap form of tamper-resistance can be provided by *software obfuscation*. Software obfuscation requires no hardware support and is implemented by adding entropy to the instructions of a program. Typically this involves adding extra code and transforming existing code so that it is difficult for humans or code analysis tools to understand, but can still be executed to produce results similar to the original program. In the past, software obfuscation has been explored and implemented, but with limited success [9]. Further, there is theoretical evidence that a general software obfuscation scheme does not exist [6]. As a result, software obfuscation is only effective against an unsophisticated adversary. Given enough time and resources, a reasonable adversary will be able to de-obfuscate the program by brute-force analysis — the reason being that if there exists a machine that can execute the code, then there likely exists another machine, possibly more complex, that can decode its operation.

A stronger way of obfuscating software is to encrypt the executable with a computationally strong cipher that will thwart a brute-force attack. Some proposals do this by placing cryptographic functions in the memory controller hardware [21, 22]. However, such systems are prone to software-based attacks — because the execution of the program is not protected, an attacker may examine the dynamic state of a program using a debugger or other such tool, and surmise the instructions that are being executed. While this requires slightly more intelligence on the part of the adversary, it is not a major hurdle for attackers. Such systems fail because there is no concept of *isolation* between different programs running on the processor.

The simplest way to provide isolation is to simply execute the tamper-resistant code on another processor. Systems described in [59, 62] support security through the use of *secure coprocessors*. These coprocessors are used to execute tamper-resistant portions of programs and are placed in physically hardened packages to prevent tampering by an adversary. The limited programming interface protects programs against software-based attacks while the physical packaging defends against hardware-based attacks. However, these coprocessors typically run much slower than the rest of the system and must be provided with their own memory and I/O interfaces. As a result, this security comes at the cost of both decreased performance and additional hardware.

The performance and hardware cost can be reduced by incorporating the features of the secure coprocessor into the main processor. Systems such as these combine architectural methods such as access control tags to protect code and data while it is on the main processor, and cryptographic techniques to protect code and data while it is in memory or on disk [35, 39]. The modifications are generally restricted to the main processor. The physical security relies on the hardening of the main processor package, but does not trust anything out of that package.

To support copy and tamper-resistant software, we propose a set of processor extensions, which are called "XOM", pronounced "zom", an acronym for eXecute-Only Memory. We create a mechanism, where code stored on disk or other media can be made so that it can only be executed, but cannot be read or modified, making it tamper-resistant. Such code, which is referred to as "XOM code" will only execute on certain hardware. In other words, the code *authenticates* the hardware it is running on. This authentication, combined with the fact that the code cannot be read, makes it copy-resistant.

The design of such systems must address issues with security, performance and flexibility. First and foremost, the system must meet its security requirements. This dissertation assumes a sophisticated adversary who has a wide variety of software and hardware tools available to her. She can execute code in privileged mode as the operating system. She can also use hardware techniques to modify and observe values in memory. The XOM hardware must be able to defend against all such attacks. Second, XOM must also operate at a reasonable level of performance. It is difficult to quantify what performance cost is reasonable for such a high level of security, so this work aims to keep the cost as low as possible without compromising the security of the system. Finally, XOM must provide flexibility. Facilities must be provided for programs to perform operations that they would be able to perform in a regular system without XOM, so long as those operations are compatible with the security requirements of the system. In other words, XOM should not impose any unnecessary restriction on software the utilizes its tamper-resistant support.

In this dissertation, we find that highly tamper-resistant software that can even defend against a compromised operating system, requires that some amount of specialized hardware be added to the processor. We will show that such hardware is modest in size and has a modest impact on performance. We do this by proposing a hardware architecture and studying its performance via a simulator, and its security via formal verification methods.

### **1.1** Overview of this Dissertation

This dissertation comprises six chapters. This chapter introduced the problem and gave a brief overview of the design space. Chapter 2 will introduce some of the concepts discussed in this dissertation. It will talk about the cryptographic mechanisms that are used, as well as *compartments*, which are logical containers in which we place our tamper-resistant software. They are what provides the *isolation* that allows programs to execute free from unauthorized observation or modification.

We then proceed to present the hardware we need to support copy and tamper-resistant software. The XOM processor bases its security in hardware, so we discuss the hardware mechanisms that we use to extend a standard processor to enable it to support compartments. These involve a combination of the cryptographic methods discussed in Chapter 2, and architectural methods such as tags and caching. In Chapter 3, we discuss the functionality required by defining an abstract XOM machine. We then discuss implementation alternatives, as well as a cycle accurate simulator that was constructed.

Operating systems inevitably have errors in them that make them vulnerable to attack. Under XOM, applications trust the processor to protect their data and execution, but do not trust the operating system. However, sharing hardware resources among multiple users is

#### 1.1. OVERVIEW OF THIS DISSERTATION

a difficult task, often requiring complex policy decisions. Thus, resource management is most naturally done in software by an *operating system*. Chapter 4 discusses the implementation of an untrusted operating system on the XOM architecture. Using the simulator discussed in Chapter 3, this chapter also presents the performance results for our modified operating system running a set of test applications.

However, while the implementation and performance may be reasonable, the XOM architecture is off little worth unless its security can be justified. In Chapter 5, we discuss the attack model XOM defends against, and discuss the mechanisms XOM uses to defend against an adversary. The security is analyzed using *formal verification* techniques in the form of a model checker.

Finally, we make our conclusions in Chapter 6 and propose future work that may be of interest.

## **Chapter 2**

## **Cryptographic Concepts**

This chapter discusses some cryptographic concepts that are used in this dissertation. XOM protects programs by controlling access to the program code and data. Access Control Lists, the natural data structure for performing this task, are well understood. However, XOM uses a slightly different abstraction, called a *compartment* [53]. The origin and motivation behind using compartments will be discussed in Section 2.1. XOM uses standard architectural tags to implement compartments for values in the trusted hardware of the processor. To extend this control into untrusted storage such as memory or disk, XOM uses cryptographic techniques, specifically symmetric ciphers, asymmetric ciphers and message authentication codes. These will be discussed in turn in the following sections.

### 2.1 Compartments

The purpose of XOM is to control access to data and code such that a program with the appropriate rights can access the code for execution, as well as the static and dynamic data the code requires. At the same time, XOM should both hide the value of that code and data from adversaries, and prevent such an adversary from modifying those values. Normally, access control refers to guarding data, but in this case, XOM is protecting an active principal such as a program together with its data. This kind of access control is more appropriately called *isolation*. In [53], Saltzer and Schroeder define *complete isolation* as:

#### 2.2. SYMMETRIC CIPHERS

Complete Isolation: A protection system that separates principals into compartments between which no flow of information or control is possible.

The operations XOM performs to protect programs provide isolation by implementing these compartments. When data is in a compartment, we say that the compartment *owns* that data. Since programs are active principals inside a compartment, we may also say that the program owns the compartment (and by extension, all the data inside the compartment). One should note that *complete* isolation means that *no* flow of information is possible. For practical systems, this is too restrictive since even programs that *want* to share information would not be able to. To implement a more pragmatic form of isolation, XOM provides a *shared compartment* that acts as a common medium available to all programs for information sharing. In contrast, all other compartments are called *private compartments*. Programs must explicitly move information between their private compartments and the shared compartment. Thus, private compartments are isolated from the shared compartment, but not vice-versa. If two programs wish to communicate information securely, they may do so by negotiating a shared secret key and treating the shared compartment as an insecure channel.

### 2.2 Symmetric Ciphers

Ciphers are algorithms that are used to obscure information in a way that only a principal who knows a certain value, called a *key*, can recover the original message. Information in its plain form is called *plain text*. The act of obscuring this information is called *encryption* and produces *cipher text*. The strength of modern ciphers is grounded on principles that are beyond the scope of this dissertation. Instead, we make common cryptographic assertion that the strength of ciphers is based on the length and secrecy of the keys.

Symmetric ciphers are a class of ciphers that use the same key for encryption and decryption. The sender uses the key to encrypt a message and send it to the receiver. The receiver then uses the key to decrypt and recover the original message. An adversary eavesdropping on the conversation will not be able to understand the message because she does not know the key that the sender and receiver share. Some common examples of symmetric ciphers are 3DES [5] and Rijndael [13]. Symmetric ciphers typically operate by permuting elements within the message, and by non-linear substitutions with the use of lookup tables. As a result, efficient hardware implementations of symmetric ciphers are possible. However, the draw back is that encryption and decryption are performed with the same key. This means that these ciphers can only be used if the sender and the receiver already share a secret key. *Key distribution* becomes a problem that is often solved by asymmetric ciphers, which are discussed in the next section.

### 2.3 Asymmetric Ciphers

Asymmetric Ciphers use a different key for encryption and decryption. The encrypting key is called a *public key* while the decrypting key is called a *private key*. The private and public key pair are randomly created during a *key generation* phase and then are stored for use after that. The principal that will receive the protected data (receiver) will generate one such pair and distribute the public key. Everyone, including the sender of the protected data (sender) and the adversary know the value of the public key, but not the private key. For this reason, asymmetric ciphers are also commonly referred to as public key ciphers. If a sender wants to send a message, she takes the public key of the intended recipient and uses it to encrypt the message. The receiver keeps the private key secret to herself and thus will be the only principal who will be able to recover the original message. An important property of asymmetric ciphers is that the public key reveals no information about the private key.

Asymmetric ciphers rely on a type of mathematical function called a "one-way trap door function." What this means is that once the function is applied, it is difficult to undo it unless there is knowledge of a special "trap door." In this case the trap door is the private key that the receiver has. For example, the El Gamal cipher [16], uses discrete logarithms as a trap door function, while RSA [50] is based on factoring. These types of functions do not lend themselves well to efficient hardware implementations, and as a result, asymmetric ciphers are orders of magnitude slower to compute than symmetric ciphers.

Typically, asymmetric ciphers and symmetric ciphers are used together to compensate for each other's short comings. A random symmetric key is chosen and the fast symmetric cipher is used to encrypt the message that is to be sent. The short key is then encrypted with the public key using the slow asymmetric cipher. The message is usually much longer than the symmetric key, and the asymmetric cipher is only used to encrypt the symmetric key for the message. As a result, for messages of sufficient length the symmetric cipher will dominate the cost of encrypting the message.

### 2.4 Message Authentication Codes

Using a cipher only prevents the adversary from learning the contents of a message. In other words, it prevents observation, but does not prevent or detect modification. Consider a scenario where an adversary substitutes some random cipher text in place of the actual cipher text in transit between a sender and a receiver. Even though the adversary cannot predict what plain text the receiver will recover when she decrypts the cipher text, the receiver will not be able to verify that the cipher text has been altered and may possibly use the incorrect data.

One could use one of the ciphers discussed in the previous sections to solve this problem. The sender can *sign* the message by encrypting it with a key known only to the sender and the receiver, and then sending both the plain text and cipher text to the receiver (note that we are not concerned about secrecy in this example, though secrecy could be acheived by encrypting with yet another key). The receiver can then verify that the plain text and cipher text match. Since only the sender knows the secret key required to create the cipher text, this prevents an adversary from *forging* the message. In this way, we provide a form of *authentication* for the message. A similar solution can be made using an asymmetric cipher instead of a symmetric one. The problem with either solution is that it is inefficient. Essentially, the message will have to double in length to include both the plain text and cipher text.

To create an efficient solution, we calculate a shorter hash of the message, and encrypt the hash of instead of the entire message. The receiver simply calculates the hash of the plain text and verifies that against the encrypted hash. A keyed hash of this type is commonly referred to as a *message authentication code* or MAC [34]. MACs are used by XOM to detect tampering of values in memory and disk.

## **Chapter 3**

## **The XOM Architecture**

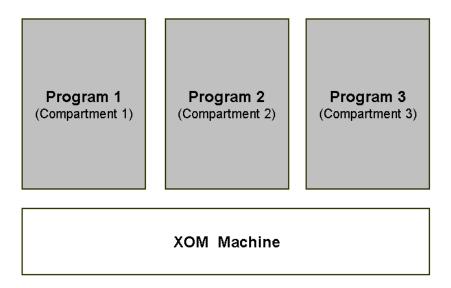

XOM uses hardware methods to provide tamper-resistance for software. The goal is to allow multiple programs, to co-exist on the same hardware, but at the same time, to provide strong guarantees that they cannot violate each other's compartments as illustrated in Figure 3.1. Though the operating system has the ability to manage resources, it is untrusted, and thus should not be able to circumvent the protection provided by the compartments.

The XOM hardware architecture implements the primitives necessary to support compartments. These primitives exist as a set of extensions that can be added to any general processor architecture. However, these extensions do not fundamentally alter the overall operation of a the system, and for the most part, the processor operates in a fashion that is very similar to the original. Regular applications will continue to be able to execute on a XOM processor unmodified. To become copy and tamper-resistant though, they must be altered to make use of the XOM extensions.

This chapter looks at the hardware and performance overheads that compartments create. It starts by describing the essential operations that a XOM machine must perform: creating, utilizing, and ultimately destroying a compartment, and protecting the compartment's memory and register data. These operations will use both asymmetric and symmetric ciphers for efficiency. We will also discuss protection in external memory, as well as implementation issues for operating systems, and effects on the distribution model for software. To better understand what is required to protect the compartments, this chapter will briefly preview the types of attacks the machine needs to protect against — but detailed

Figure 3.1: Compartments. The XOM Machine keeps each program in its own compartment. The compartments isolate the programs from each other, preventing the flow of information between them.

discussion of attacks will be deferred to Chapter 5.

The hardware required to implement this machine can be quite small, since most of the functionality can be provided by a trusted virtual machine monitor to create a virtual XOM machine. Unfortunately, this simple machine needs to encrypt/decrypt data on each memory operation. The chapter then describes how this overhead can be greatly reduced by adding tags to both the registers and the on-chip cache memory, as well as the use of hardware accelerators for cryptographic operations.

To study hardware implementation issues, we created a XOM hardware simulator. The simulator is built on top of the SimOS [28] using an architecture based on a MIPS R10000 processor [27]. We then go on to discuss issues on maintaining XOM systems, such as upgrading hardware to which software has been tied, as well as recovering software from a hardware failure. Finally, this chapter finishes with a discussion of related work that supports copy and tamper-resistance.

### **3.1 The Abstract XOM Machine**

We begin this section by describing an Abstract XOM Machine. This is a set of extensions that when added to a generic machine, allow it to securely execute code in compartments. The XOM machine implements compartments as described in Section 2.1 to isolate programs executing on the machine from each other. To implement these compartments, the XOM machine will track which compartment a particular piece of code or data belongs to. To do this, the XOM machine associates a unique identifier, called a XOM ID with each compartment. Data and code in the machine are tagged with the XOM ID of the compartment to which they belong. When code is executing in a compartment, the XOM ID for that compartment becomes the currently active XOM ID. As a result, all data accessed by that program must be tagged with the same XOM ID as the compartment, otherwise an exception occurs and the program is halted. When a program writes data to a location, the tag on that location is set to the XOM ID of the active compartment. In this way, the XOM machine associates executable code with data that is *owned* by that program in its compartment. The XOM machine extends the base processor architecture with a XOM ID register that holds the XOM ID of the currently active compartment, as well as adding XOM Compartment Tags to all registers. Operating in a compartment penalizes programs with some amount of performance overhead. As a result, the XOM machine provides programs the ability to choose whether to execute in a compartment or not. An enter xom instruction is added to the instruction set architecture (ISA) of the machine that allows programs to indicate that they are going to start executing in their compartment and that all following instructions should be protected. Likewise, an exit xom instruction executed from within a compartment indicates that the program wishes to leave protected execution. With this mechanism, a program can even execute partially protected in a compartment, and partially in the clear with no protection. The actual choice of when to execute securely and when not to depends on the characteristics of the application, as executing in a compartment incurs certain penalties that will be discussed later.

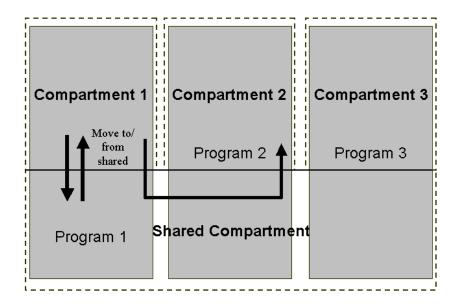

Compartments provide a way for programs to execute without fear of observation or tampering. However, the compartment also prohibits the intentional flow of information. For example, if a program in a compartment wishes to share a result with another program in another compartment, it would not be able to do so since the other program's XOM ID does not match the tags on the registers. To allow controlled communication, XOM provides a *shared compartment* as described in Section 2.1. This compartment has a XOM ID of zero and programs are by default unprotected in the shared compartment before they execute an enter xom. On an exit xom instruction, programs return to the shared compartment. To allow protected programs to use the shared compartment, the XOM Abstract Machine extends the base ISA with two additional instructions to allow communication between programs. This communication is provided by the move to shared and move from shared instructions. These instructions provide a controlled way to change the tags associated with a piece of data. The move to shared instruction takes data that is tagged with the active XOM ID and changes the tag on it to the shared XOM ID. Executing this instruction on data that is not owned by the program results in an exception. The move from shared instruction changes data tagged by the shared XOM ID to the active XOM ID. Once again data has to be tagged with shared before this instruction can be executed. These two instructions, in combination with enter xom and exit xom, allow a program to keep part of its execution and data in a compartment, while keeping another part in the shared compartment as illustrated in Figure 3.2. While in its private compartment, the program can move data back and forth between its shared and private compartments with the move to shared and move from shared instructions.

Thus, a program can transmit data from its compartment to another through the shared compartment as follows:

- 1. Program A puts the data to be shared in a register. The register is tagged with Program A's XOM ID.

- 2. Program A executes move to shared on the register, moving the data into the shared compartment. The register is now tagged with the shared XOM ID.

- 3. Program B executes move from shared on the register, moving the data from the shared compartment to Program B's compartment. The register is now in Program B's compartment.

Note that data in the shared compartment can be read by any program, not just the intended recipient. If Program A and Program B wish to ensure that the data is transmitted without

Figure 3.2: The Shared Compartment. The Shared Compartment is used as a common compartment through which programs with separate private compartments can communicate. Programs enter and exit their compartments with the enter xom and exit xom instructions, and move data between their compartment and the shared compartment with the move to shared and move from shared instructions. Data can also flow between private compartments through the shared compartment.

fear of tampering or observation by an adversary, they can set up a secure channel with a shared key.

#### 3.1.1 Supporting External Memory

A XOM machine such as the one above would require all secure code and data to fit onto the processor. This is unlikely given the size of today's programs. While it would be possible to extend the tagging scheme into memory, this presents possible security flaw. Communication between the processor and memory usually occurs on a bus implemented as traces on a circuit board. This can be probed by an adversary with methods orders of magnitude cheaper than those that would be required to probe on-chip signals [31, 49]. As a result, the XOM design must assume that any data that has been transmitted off the chip, can be potentially read or altered by an adversary. In other words, hardware that is not in the same chip package as the main processor is assumed to not be tamper-resistant. The security of tags relies on the tamper-resistance of the chip package. To protect memory we turn to cryptography. XOM encrypts data leaving the processor and decrypts it when it is loaded back onto the processor. To allow the machine to check the integrity of the data as well as protect it from observation, a MAC is associated with all values stored in memory. If an external agent tampers with the data, then the MAC will not verify and the instruction will cause an exception. As discussed in Chapter 2, encryption algorithms require a key with which to encrypt or decrypt text. As a result, every compartment must have a unique *compartment key*. Since the program code is initially in the compartment and in memory, it must be encrypted with the compartment key and accompanied by a MAC before execution. Compartment code is decrypted with the compartment key before execution. The XOM machine also uses this compartment key to encrypt and decrypt data stored by the program in memory.

Because these cryptographic operations incur some overhead, the XOM machine allows programs in a compartment to indicate whether data going to memory should be kept in the compartment and encrypted, or whether it should be left outside the compartment in plain text. This is done by adding a secure store instruction, which stores data securely to memory, and a secure load instruction, which will load secure data from memory. These do not replace regular loads and stores, which interact with data in memory without encrypting or decrypting it. The secure load instruction takes a destination register and memory location as operands. It decrypts the contents of memory using the active compartment key, verifies the MAC, loads the decrypted value into the register and changes the tag on the register to the active XOM ID. If there is a mismatch in the MAC, the instruction will cause an exception. The secure store instruction stores data to memory securely, by encrypting it with the compartment key and adding a MAC. It can only be executed on a register tagged with the active XOM ID, while a regular store can only be executed on a register tagged with the shared XOM ID. The secure store instruction encrypts the register contents as well as creating a MAC, and stores both to memory. If the register sourced in a secure store is tagged with a XOM ID other than the active one, the instruction raises an exception.

### 3.1.2 Supporting an Operating System

Now we have the essential primitives to allow a single program to run securely and use memory. However, programs must typically run alongside other programs, sharing resources on the same processor. The allocation of resources is governed by an operating system. To manage resources effectively, the operating system must be able to arbitrarily interrupt the program, store its state to memory, and then restart the program with that state at a later time. The operating system must also be able to relocate program data that is in memory. However, XOM does not trust the operating system. This is because there are many methods with which an adversary could compromise the operating system and gain control of it [10]. When a XOM program is interrupted, the contents of the registers are still tagged with the XOM ID of the interrupted program. As a result, the operating system is unable to read those values to store them to memory. We need to add two more instructions to the ISA — the save register and restore register instructions. To allow the operating system to relocate secure data in memory, we make the MACs available to the operating system so they can be moved together with the encrypted data.

The save register and restore register instructions are used by the operating system to move data that it does not own and does not belong to the shared compartment. The save register instruction takes the contents of a register and creates an encapsulated version of this data the operating system can move, but cannot manipulate. It first encrypts the register contents and then calculates a MAC that includes the identity of the register. It places the encrypted data, MAC, and the XOM identifier into a set of special registers, which are owned by the operating system. This data can then be stored to memory.

The restore register instruction is the inverse of the save register operation and it is used to restore the data back to the registers before restarting a program. The instruction uses the special registers that hold the encrypted data, MAC, and destination key identifier. The operating system then indicates with the instruction, which register and what compartment XOM ID it wishes to restore the register value to. The XOM machine decrypts the data and checks the MAC. If the MAC verifies both the decrypted data and

#### 3.1. THE ABSTRACT XOM MACHINE

| Instruction      | Description                                                 |

|------------------|-------------------------------------------------------------|

| enter xom        | Enter secure execution and set the currently active XOM ID  |

|                  | to the current compartment. All following instructions are  |

|                  | in the compartment and should be encrypted and accompa-     |

|                  | nied by a MAC.                                              |

| exit xom         | Exit XOM compartment and return to the shared compart-      |

|                  | ment. Set the currently active XOM ID to shared.            |

| secure store     | Stores register to memory securely.                         |

| secure load      | Loads memory securely from memory to a register.            |

| save register    | Encrypts and saves a register to memory so that the operat- |

|                  | ing system can save a program's state.                      |

| restore register | Decrypts a value from memory and places it a register to    |

|                  | restore a program's state.                                  |

| move to shared   | Sets the XOM ID tag of register to the shared compartment.  |

| move from shared | Sets the XOM ID tag of register to that of the executing    |

|                  | program.                                                    |

Table 3.1: Instructions in the Abstract XOM Machine. This table summarizes the instructions that the XOM Abstract Machine adds to the base instruction set architecture.

destination register were not tampered with, the decrypted data is written into the destination register and the register tag is set to the target XOM ID. In this way, we ensure that the register contents are not altered and that the values are restored back to the same register from which they were saved.

The other issue is to enable the operating system to relocate data that has been stored and encrypted in memory. This is done by making the MACs stored by the XOM processor available to be copied or moved along with the encrypted data. Thus when the operating system wishes to relocate values in memory or swap them to disk, it copies both the MAC and the cipher text together. This does not require any special instructions as the cipher text in memory can be handled with regular memory operations.

At this point we have described all the instruction set additions XOM needs to make to the underlying architecture. We summarize these instruction in Table 3.1. We will now discuss how this architecture affects the software distribution model. Further, we will discuss the security of the XOM machine, by examining the types of attacks XOM defends against.

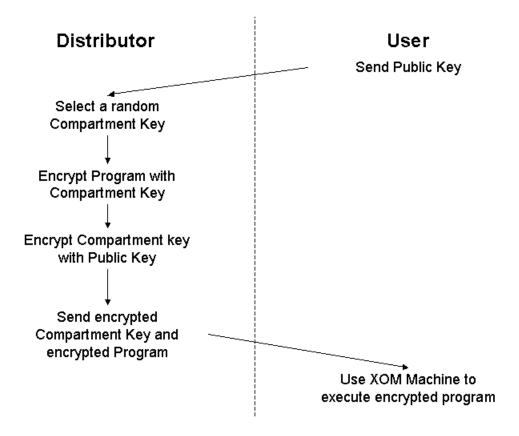

#### 3.1.3 Software Distribution Model

Since programs are typically created on a system other than the one that will execute the program, the compartment keys must be transmitted from the program producer to the processor that does the execution. Asymmetric ciphers are the perfect tool to accomplish this. Figure 3.3 illustrates a flowchart for this process. By hiding a private key in the hardware of the processor and distributing the public key, programs have a way of transmitting the compartment key to the processor for execution. As discussed in Section 2.3, the software producer simply encrypts the program image with the compartment key, and then encrypts the compartment key with the public key of the target processor. Since this private key is used to protect all compartment on a machine, it is referred to as the *master secret*. If every XOM machine is initialized with a different public/private key pair, then this provides a way for a program to authenticate the processor it is executing on, as it will only be possible for the processor with the correct private key to decrypt and access the compartment key. This provides copy protection for programs. Without the compartment key, a processor cannot decrypt and execute the program. Without knowledge of the master secret, even an adversary with sophisticated virtualization or simulation technology, will not be able to fake or forge a XOM machine, and fool software into executing.

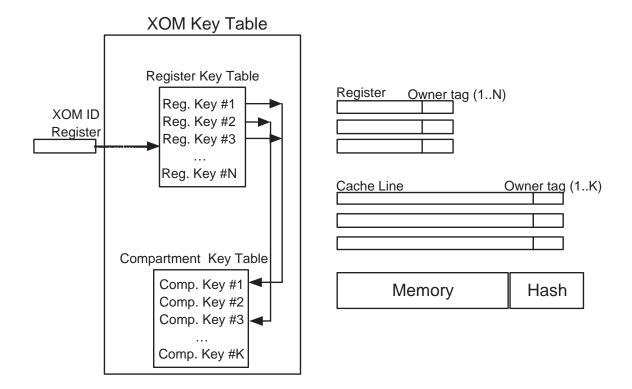

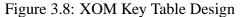

To execute compartment code, the XOM processor must first decrypt and recover the compartment key. As a result, what the enter xom instruction actually does to enter the compartment, is to decrypt the compartment key with the private key or master secret of the XOM machine, and then assign a XOM ID to it. The decrypted compartment key is then stored in a hardware table called the *XOM Key Table*, which maps the compartment keys onto XOM IDs. The XOM machine uses the XOM Key Table to find the appropriate compartment key to decrypt instructions and for use with the secure load and secure store instructions. For example, during a secure load the XOM machine does a lookup on the XOM Key Table using the value in the currently active XOM ID register. With this, it gets the correct compartment key, and uses that to decrypt the value that is coming from memory.

The exit xom instruction unloads the compartment key from the XOM Key Table. This frees up entries in the XOM Key Table for use by other programs. However, this opens

Figure 3.3: Software Distribution in XOM. The software distributor uses asymmetric keys to transmit the compartment key to the processor. The processor can then recover the compartment key and use it to execute code inside the compartment.

up a potential security hole. An entry in the XOM Key Table could be freed and reallocated to another compartment, and it is possible for the new compartment to be assigned the same XOM ID as the previous compartment. The new compartment could thus gain illegitimate access to data belonging to the old compartment due to recycling of the XOM ID value. To ensure that the new compartment doesn't gain unauthorized access to data in the previous compartment's data, the XOM machine clears all registers that are tagged with a XOM ID before it can be allocated to a new compartment.

XOM affects the commercial model for software distribution. For a given program, a compartment key must be encrypted specifically for each processor. As a result, the distributer will typically encrypt all copies of the program with a single compartment key and distribute the encrypted copies. When a customer wishes to purchase the software, as part of the installation process, she contacts the software distributor to pay for or register the software. At this point, the distributor will return a compartment key specifically encrypted for the customer's processor after he is satisfied that the customer has paid for the software.

One issue where key distribution is a bit more complicated is if multiple CPUs execute the same binary. This is the case in systems with multiple processors. Multiprocessor systems have several CPUs that share a common pool of physical memory and are managed by a single operating system image. As a result, each CPU has to be able execute the same encrypted binaries. However, each XOM CPU has a different master secret. To allow all CPUs to run the same binaries, the compartment key is encrypted separately for each CPU and software support is added so when a thread wishes to allocate a XOM Key Table Entry, it allocates it with the compartment key encrypted for the CPU it is running on.

XOM also affects the software development process. Software developers use debugging tools inspect or even alter the state of running programs during development. XOM would prevent any of these debuggers from working since the processor is unable to differentiate between a valid user trying to debug a program and a malicious attacker trying to use a debugger to extract secrets from a program. The solution is to note that the developer should know the value of the compartment key. With this knowledge she may decrypt and alter values in memory. In addition, with knowledge of the compartment key, she can construct a program that can inspect and alter the register state of the program being debugged. This can be done with a technique akin to that used to create user-defined signal handlers as explained in Section 4.4.3

#### 3.1.4 Security

The Abstract XOM Machine has a number of useful capabilities at this point. It can support the execution of programs protected in private compartments. It also allows the use of an untrusted operating system to manage resources for such programs. Next, we will examine some common attack strategies that an adversary may employ and see how the XOM machine defends against them.

#### 3.1. THE ABSTRACT XOM MACHINE

Simply encrypting data in memory is not sufficient to make it tamper-resistant. Encryption only ensures the secrecy of the data in memory, but does not guarantee its integrity — an adversary can still alter values randomly in memory. To address this, the XOM processor adds a MAC to every piece of data that is written to memory and verifies this MAC for both data and instructions that are read from memory as mentioned in Section 3.1.1.<sup>1</sup> The MAC is then stored to memory at the same time the cipher text is. Taking a MAC of the data prevents an adversary from substituting tampered data in the place of real data. This attack is referred to as a *spoofing attack*. Because the adversary cannot create a valid MAC, she cannot forge a valid piece of data in memory.

A slightly more complex attack is one where the adversary does not need to create a fake cipher text and MAC. Instead, she simply copies both the cipher text and the MAC from one memory address to another. We refer to this as a *splicing attack*. A splicing attack is countered by including the virtual address along with the data in the pre-image<sup>2</sup> of the MAC. Thus, when verifying the hash, the XOM machine can ensure that the data it is being loaded from the same virtual address it was originally written to. Since the virtual address must be included in the pre-image for the MAC calculation, the caches must be extended to include the virtual address of the data in each cache line.

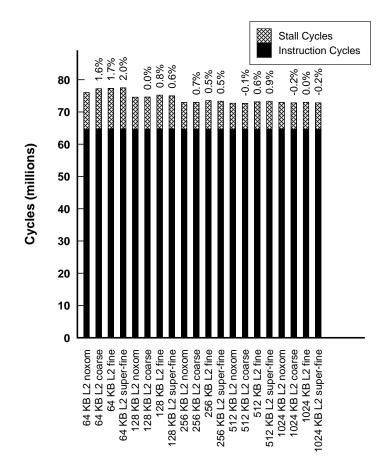

Still another attack exists for a determined adversary. This attack involves the adversary recording cipher text and MAC values at a point in the execution of a program and then "replaying" them at a later point in the execution of the same program. This attack is aptly named a *replay attack*. An adversarial operating system is capable of performing this attack on both register and memory values. To replay a register value, the adversarial operating system interrupts a running process and saves the register state using the save register instruction. The adversary than restores the process state and restarts the process. At a later time, the adversarial operating system interrupts the process again, but instead of restoring the register values from the second interruption, it restores the values from the first interruption. When the process restarts, it will be using the replayed register values. To defend against such an attack, the XOM machine uses a key other than the

<sup>&</sup>lt;sup>1</sup>If desired, a separate key could be used for the MAC, and everything would still follow, but we do not discuss that here.

<sup>&</sup>lt;sup>2</sup>The pre-image is the value that is used in the hash calculation.

compartment key for encryption in the save register and restore register instructions. This key, called the *register key*, is regenerated every time a particular XOM compartment is interrupted. As a result, the register key that is used to save the register at the time of the first interrupt, will have been destroyed and regenerated when the adversary tries to restore the state from the second interrupt. Thus, trying to restore the stale value will result in an exception.

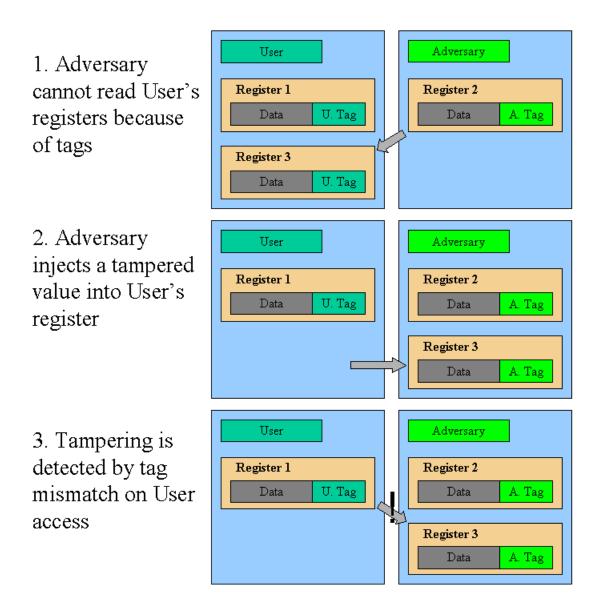

Instead of trying to replay values in registers, an adversarial operating system may try to replay data in memory. To do this, the operating system records cipher texts and MACs in memory and then overwrites the same location at a later time with the old cipher text and MACs. To defeat this attack the application keeps a hash for a region of memory in one of the registers. To replay this region, the adversary must also be able to replay the hash kept in the register. However, the regenerating register key will protect the register from replay, thus defeating the memory replay attack. The drawback with this approach is that every time a value in the region changes, the hash kept in the register must be updated. If the region of memory is large, or if the values in this region change frequently, this results in a large overhead as the entire region must be read to update or verify the hash. The performance impact can be mitigated by using Merkle trees to perform memory authentication. For now, we will defer the discuss Merkle trees to Section 5.2.

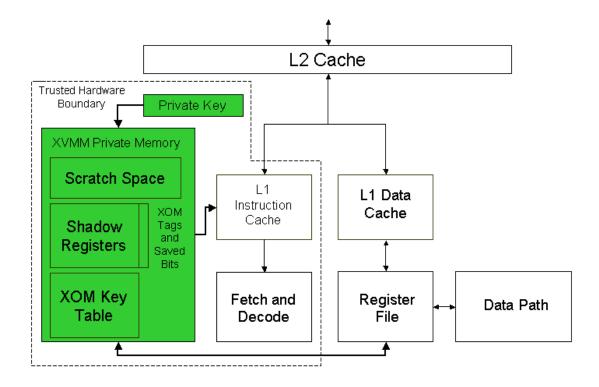

### **3.2** Virtual Machine Implementation

A XOM machine can be implemented as a virtual machine with a minimum amount of hardware. Such a virtual machine would operate between the operating system and the hardware. The XOM virtual machine takes the underlying hardware and presents a XOM Abstract Machine image to the operating system. However, a virtual machine that uses emulation often suffers slow downs on the order of 3-13 times [64]. The performance will be substantially improved with the implementation of a *XOM Virtual Machine Monitor (XVMM)*. With a virtual machine monitor, software is compiled for the underlying hardware, and runs natively on the underlying hardware for the most part, with the processor hardware invoking the virtual machine monitor only when certain events occur. Virtual

machines have been implemented in the past without additional hardware [8, 24, 63]. However, supporting the security features of XOM in a virtual machine monitor does require a small amount of extra hardware.

The main hardware additions to the CPU include special microcode that stores the private key, private on-chip memory, the ability to trap on instruction cache misses and a special privileged mode under which the XVMM runs. The actual XVMM could be implemented in either software or in microcode. Software implementations must be authenticated by a secure booting mechanism such as those described in [37, 61, 62]. Either way, the XVMM executes as a trusted, authorized, and privileged program. There are special hardware facilities that only the XVMM can access, such as the private key, secure on-chip memory and the revectoring of certain interrupts. This is why the XVMM must run at a privilege level higher than that of the untrusted operating system.

A XVMM implementation also requires the hardware to invoke it on certain events. When a program in a XOM compartment misses in the instruction cache, the XOM machine must fetch the required instruction from memory. The XVMM must be invoked by the hardware on instruction cache misses so that it may decrypt the data coming from memory and place it in the cache. In this way, the XVMM can use the instruction cache to hold decrypted instructions. This is possible because *all* instructions in a compartment must be encrypted. However, an XVMM cannot store data in plain text in the data cache. Because compartments have the ability to choose whether data is stored to the compartment, via the secure store instruction, or stored to the shared compartment using a regular store, the XVMM would have no way of telling what compartment data in the caches is in, without additional hardware in the data cache.

An XVMM requires the processor to be configured to trap on instruction cache misses so that the XVMM may decrypt data and instructions that are coming from memory. An *informed memory operation* [30] is a mechanism that interrupts the processor on all cache misses, and can be used to implement the control transfer required for our XVMM. The XVMM configures the informed memory operation to transfer control to code specific to the memory operation that missed. This code will then perform the required decryption to recover the instructions for execution.

Data in the machine (such as caches and registers) must be tagged in some way to

implement compartment access control. The obvious solution is to add a hardware tag to each unit of hardware storage that requires one. However, this additional hardware is not strictly needed by an XVMM. Instead of explicitly adding hardware tags, the XVMM could simply remove the compartment data from the machine every time the program leaves a compartment (either due to an explicit exit xom instruction, or implicitly due to an interrupt). This is done by flushing the instruction cache and clearing all registers.

Flushing the instruction cache ensures that instructions that have been decrypted and placed in the cache are executed after the program leaves its compartment. Because the instruction cache contains no modified data, clearing the contents is a straightforward operation. However, clearing the registers requires support from the XVMM. A shadow register file is needed to hold data required for XOM instructions such as move to shared and move from shared, as well as register save instructions save register and restore register. The XVMM maintains a set of shadow registers for the each compartment in the XOM Key Table. These are managed entirely by the XVMM, requiring no special hardware support. The shadow registers store the value as well as an ownership bit indicating whether the register is in the private or shared compartment. The move to shared and move from shared instructions cause the XVMM to update the ownership state in the shadow registers from owned by the private compartment to owned by the shared compartment. When a compartment is interrupted, the XVMM moves data that is owned by the compartment from the registers into the shadow registers, thus preventing illegal access by the operating system's interrupt handler. Later, when the operating system restarts the compartment, the XVMM moves the data from the shadow registers back to the actual registers.

The limitation of this model is that the XVMM cannot unambiguously differentiate between an operating system that legitimately alters the register state of a compartment, from one that does so maliciously. For example, the operating system may interrupt a XOM program running in a compartment, and store the register state of the compartment using register save instructions. However, it might not restore a certain register when it restarts the compartment, but may instead leave a value of its choosing in that register. The XVMM cannot safely restart the process in this case since the unrestored register may hold tampered data, which could be used by the compartment code if restarted. A conservative

Figure 3.4: The XOM Virtual Machine Monitor (XVMM). The XVMM requires some additional hardware in the form of storage for the masters secret (private key) and private memory for the XVMM to use.

solution would be for the XVMM to refuse to restart the compartment, until the operating system restores the state of all compartment registers using the restore register instruction. However, this would prevent the operating system from returning data from after an exception, as it may do after a system call. The solution to this is to note that during an asynchronous interrupt, the operating system has no reason to alter the register state of the interrupted compartment. However, on a synchronous interrupt such as a system call, the compartment knows a priori, that a certain register will have a return value in it. As a result, the burden is placed on the compartment to make sure the result register has had its ownership changed to shared with the move to shared instruction before a system call. Otherwise, the operating system will not be able to set the return value. This burden on the application can be removed with additional hardware as we see later.

The additional hardware and structure of the XVMM is summarized in Figure 3.4. The

XVMM implements the instructions as follows:

enter xom: The program indicates an address where the XVMM will find the program's encrypted compartment key. The XVMM loads the encrypted compartment key and performs an asymmetric decryption to recover the compartment key. The XVMM then stores the compartment key into the XOM key table, assigns a XOM ID, and notes that this is the "currently active XOM ID". Instructions after an enter xom must be encrypted and accompanied by a valid MAC, otherwise the XVMM will not load them into the instruction cache for execution. The XVMM initially assumes all registers are in the shared compartment after an enter xom. The program must indicate to the XVMM which registers it will use to store private data with the move from shared instruction.

The XVMM registers a handler for cache miss events so that instruction cache misses incurred during the execution of XOM code will be correctly vectored to it. Similarly, it also re-vectors all CPU exceptions and interrupts to itself. If the compartment takes an exception that must be delivered to the operating system, the XVMM copies all registers that are in the private compartment into the set of shadow registers corresponding to that compartment. Naturally, if the compartment was active, the program counter is one of the registers that the XVMM saves. Finally, before execution of secure code, the instruction cache is flushed to clear out any instructions that are not in the compartment. Later, when the operating system returns execution to the user process, the XVMM must again be invoked. It restores the private registers from the shadow registers for the compartment, but leaves the registers in the shared compartment untouched. This allows the operating system to modify some user registers in order to to handle events such as system calls.

**exit xom**: The XVMM unregisters the handler for cache miss faults and restores handlers for all CPU interrupts and exceptions. The contents of the instruction cache are flushed.

**secure store**: The XVMM ensures that the register is marked as private in the shadow register file. Then it encrypts the register and calculates a hash. Both the register and hash are stored to memory.

**secure load**: The XVMM decrypts the value from memory and verifies it against the hash. If this operation succeeds, the value has not been tampered with and is written into the register. The status of the register in the shadow register file is set to private.

**move to shared**: The XVMM verifies that its shadow registers indicate that the register is currently in the private compartment. If it is not, the XVMM raises an exception. Otherwise, it tags the shadow register as shared.

**move from shared**: The XVMM checks that the register is currently marked as in the shared compartment in its shadow registers. If so, it marks the register as being in the private compartment.

**save register**: When the compartment is interrupted, the XVMM moves all values marked private in the shadow register file from the architectural registers into the shadow registers. However, the XVMM still must note which registers were saved by the operating system so it knows which ones to restore when restarting that compartment. To do this, it keeps another bit, called the *saved bit* for each register in the shadow register file the XVMM maintains for each compartment. On an interrupt, the XVMM clears all the saved bits in the shadow register file of the compartment. When the operating system executes a save register instruction, the XVMM sets the saved bit for the corresponding register in the shadow register file.

**restore register**: When the operating system uses the restore register instruction to restore a register value, the XVMM clears the saved bit in the shadow register file, indicating that the register is to be restored when the compartment is restarted. When the operating system restarts the XOM program, the XVMM checks that all saved bits are cleared in the shadow register file. If any are still set, the XVMM throws an exception. This prevents the operating system from injecting data into the compartment. If all saved bits are cleared, the XVMM copies all private registers from the shadow register file to the architectural registers and restarts the compartment. Any registers not marked private in the shadow register file are left unaltered.

The XVMM trades off performance for a simpler hardware implementation where most of the complexity is moved to software. The additional hardware requirements are secure storage for the private key and some on-chip memory that the XVMM can use for its private data structures.

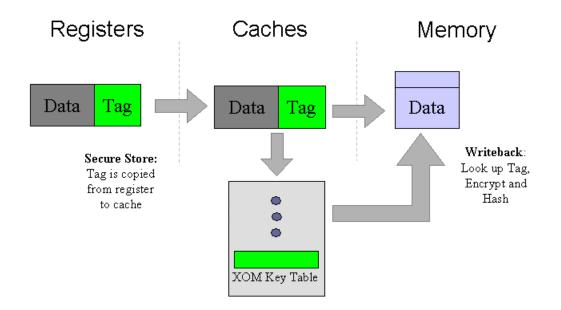

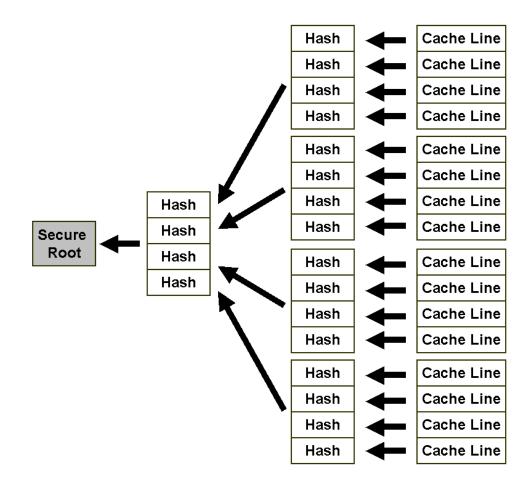

Figure 3.5: Memory Support for Secure Store. Data is first stored into the cache. On cache eviction, the XOM Cache Ownership Tag is used as an index into the Compartment Key Table. The appropriate compartment key is then used to encrypt and MAC the data.

## **3.3 A Hardware Implementation of a XOM Machine**

The XVMM described in the previous section suffers from three main performance penalties which can be mitigated with extra hardware. The first is that the XVMM is unable to cache compartment data, only instructions. In addition, the XOM machine must flush the instruction cache every time there is a trap. Both problems can be fixed by adding XOM ownership tags to the on-chip caches. The second source of overhead is the fact that the cryptographic operations are handled in software by the XVMM. Selecting fast algorithms and adding hardware acceleration reduces the cost of these operations. The final source of overhead is that the instructions that XOM provides are interpreted as opposed to implemented in hardware. A full hardware implementation would remove the need to trap to the XVMM as those operations would be handled directly in hardware.

The performance overhead of the memory encryption and MAC computation can be

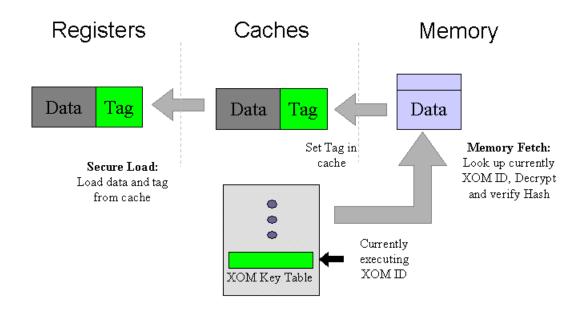

Figure 3.6: Memory Support for Secure Load. On a cache hit, the data is simply loaded from the cache. If the load misses, the cipher text and MAC is decrypted, verified and placed in the cache.

reduced by adding XOM compartment tags to the on-chip caches. Tags allow the processor to track the ownership of values in the caches, thus enabling the machine to cache data valves, and removing the need to flush the instruction cache on traps. This allows the XOM processor to utilize the on-chip data cache to defer encryption until the data is flushed to memory and also means that data or instructions need only be decrypted once as they are loaded from memory into the cache. Caching effectively reduces the number of cryptographic operations, meaning the program need only pay the cost when it misses in the cache. The overhead of the cryptographic operations are also reduced by tagging a cache line rather than a single data word. This larger block size reduces initialization overhead of the operations and also reduces the space overhead for the MACs as each MAC is protecting a larger section of memory.

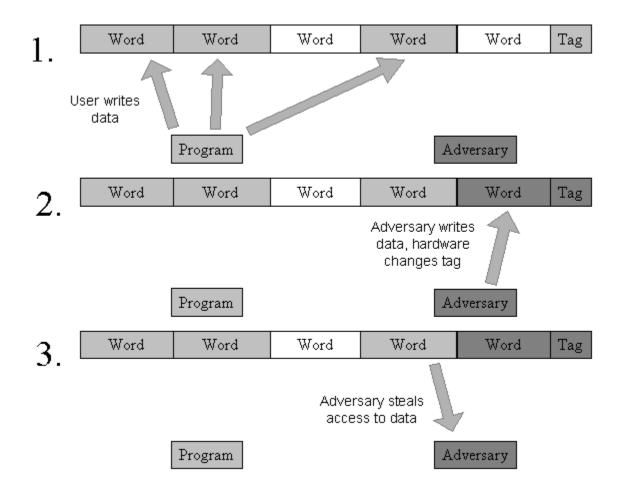

Tagging cache lines and not individual words also introduces a security complication. There is a XOM ID tag for every register, and a XOM ID tag for every cache line. But a cache line typically contains several words, so as a result, the granularity of compartment ownership in the registers is different from that in the caches. This poses a security threat that allows an adversary to take ownership of data that does not belong to it. If the XOM machine naively sets the XOM ID to the last compartment that writes the cache line, this would allow an adversary to take ownership of all the data in a cache line by writing to a single word within that line. This attack is illustrated in Figure 3.7. Clearing the cache line with some value (such as zeros) before allowing the new owner to write to the line does

Figure 3.7: Valid Bits in the Caches. A clever adversary exploits that difference in protection granularity between registers and cache lines. The attacker writes to a single word to take ownership of all words in the cache line.

not solve the problem, as this would allow an adversary to arbitrarily inject values (such as zeros) into the compartment of the previous owner. The solution requires additional hardware to be added in the form of per-word valid bits in the cache. Valid bits are added to each cache line to indicate which words in the line are valid and which are not. When the XOM ID of a cache line changes, all valid bits are set to invalid, and only become valid when that particular word is written by the new owner. Data which is set to invalid in this way is lost. This implies that for correct operation, two compartments *cannot* share a cache line as each time the line changes ownership, the previous owner's data will be clobbered. When a cache line is flushed to memory, the valid bit information must also be stored along with the MAC and then returned when the cache line is loaded back into the cache, otherwise the adversary could get rid of the valid bit state by simply causing the line to be evicted.

Adding tags to the caches also introduces another problem. Naively implemented, a XOM application that forks will cause the operating system to create a child that is the exact copy of the parent, with the child inheriting the parent's XOM ID value. If the operating system interrupts one process, say the parent, and restores the other, an error will occur since the current register key will not match the register state of the child.

The solution is to allocate a new XOM ID for the child. Because there are two different threads of execution, we need two different register keys (and two different XOM IDs). Register data is tagged with XOM IDs, which distinguish between the compartment of the parent and the child. The situation with the data in the cache is more subtle. Since both parent and child have the same compartment key, secure data in the caches must be tagged with the same value for both. Clearly, we cannot use the XOM ID tag, which is different for each process; instead a different set of tags, cache ownership tags, are used in the caches.